企業博客

更多>>有源晶振負電阻測量

來源:http://www.bsgccc.com 作者:康比電子 2019年01月07

有源晶振型號眾多,而且每一種型號的引腳定義都有所不同,接法也不同.有源晶振的使用極其廣泛,但凡在電子產品中都會出現它的身影,使用在普通家電,普通電器,智能化產品,科技產品等電子相關產品.有源晶振是用石英晶體組成的,石英晶片之所以能當為振蕩器使用,是基于它的壓電效應:在晶片的兩個極上加一電場,會使晶體產生機械變形;在石英晶片上加上交變電壓,晶體就會產生機械振動,同時機械變形振動又會產生交變電場,雖然這種交變電場的電壓極其微弱,但其振動頻率是十分穩定的.下面康比電子本篇文章主要了解有源晶振的振蕩器的一些知識.

下面介紹由晶體單元組成的典型振蕩電路.例如,使用的元素常數.

CL=(C1xC2)/C1+C2)+雜散電容

雜散電容可在2pF到6pF之間變化. 1. 當在C-MOS振蕩電路中使用時,電路圖中的Rd是必不可少的,以將驅動電平保持在規定值內并獲得穩定的振蕩頻率.

2. C1和C2應在10~31pF的范圍內使用.如果在低于或高于30pF的情況下使用C1和C2,則振蕩可能容易受到電路條件的影響,驅動電平可能增加或負電阻可能降低,從而導致不穩定的振蕩.

3. 晶體振蕩電路的布局應盡可能短

4. 應減少電路和接地圖案之間的雜散電容.

5. 應避免晶體振蕩電路圖案在其他電路圖案上的交叉.

6. 超聲波清潔可能導致有源晶振晶體單元的劣化.

.png)

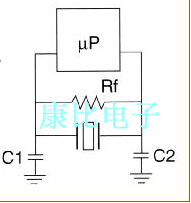

圖A

應用說明:為微處理器選擇晶振

除非在微處理器數據表中另有規定,否則本應用筆記可用作選擇晶振的一般指導,該晶體可與許多領先的微處理器制造商一起使用.

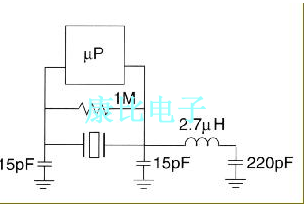

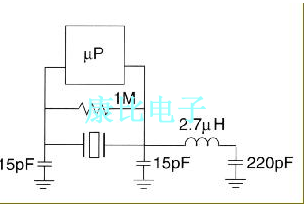

大多數微處理器都包括一個帶正反饋電阻(典型值為1MO)的逆變器設計,帶有一個可選的串聯電阻,其值在10歐姆到1K歐姆之間變化(見圖A)

它具有輸入端口(通常稱為XIN,XI,XTALI或類似性質)和輸出端口(XOUT,XO,XTALO或類似性質),用于這兩個端口之間的晶體單元連接.大多數芯片都設計有一個選項,可以通過外部時鐘振蕩器驅動,輸入到晶體輸入端口,也可以使用外部晶振.

根據共振頻率,可以選擇晶體作為基波或泛音模式.通常,28MHz以上的頻率需要第三個泛音模式以獲得價格優勢和交付.

在并聯模式中,石英晶振電抗是電感性的,需要兩個外部電容器(C1)和(C2)來實現必要的振蕩相移.無論晶體處于基模還是泛音模式,都需要C1和C2.C1和C2的值由芯片制造商規定,從6pF到47pF不等.

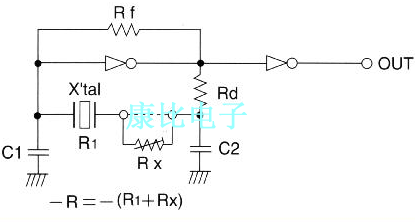

C1和C2可能不平衡,即值相等,但有時會以特定比率(C1/C2)偏移以獲得最佳性能,具體取決于晶體和放大器特性以及電路板布局.圖B示出了基模操作的典型配置.

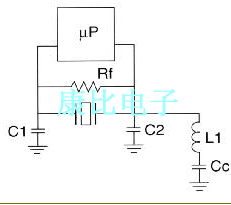

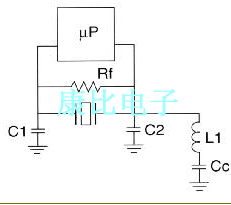

在泛音模式中,需要附加電感器L1和電容Cc來選擇第三泛音模式,同時抑制或拒絕基模.選擇第三泛音晶體電路中的L1和Cc值以滿足以下條件.

來自串聯諧振電路的L1,Cc分量的頻率低于基頻,這使得電路看起來在基頻上是電感性的.這種情況不利于基模的振蕩.

來自并聯諧振電路的L1,Cc和C2分量的頻率大約在基波和第三泛音頻率之間的中間.這種情況使電路在第三泛音頻率處電容,這有利于在所需的泛音模式下的振蕩.(見圖C)

圖C

在標準泛音模式下,C2值從10pF到30pF不等.Cc值應選擇至少為C2值的10倍,因此其等效C-equiv.將近似值.

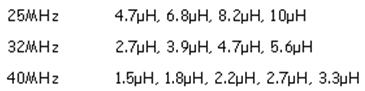

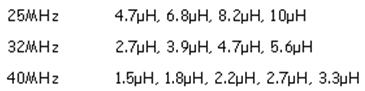

不同晶體頻率的L1典型值:

圖D示出了40.320MHz,第三泛音模式操作的典型電路配置.

圖D示出了40.320MHz,第三泛音模式操作的典型電路配置.

圖D

應用說明:負電阻測量

當晶體單元作為振蕩電路中的感應無功電抗被驅動時,晶體單元和振蕩電路之間的關系如圖E所示.為了改善振蕩電路的啟動條件,可以增加振蕩電路的值.負電阻-R-振蕩電路的哪個參數.如果沒有很多負電阻(較小的負電阻)的電路與具有較大諧振電阻的貼片晶振晶體單元組合,則起始條件將變得更糟.振蕩電路的設計目標應使負電阻值為諧振電阻的5至10倍. 還需要將負載電容的中心值(確定振蕩頻率的絕對值)和可變范圍(振蕩頻率的微調范圍)保持在振蕩電路中的最佳值.

負阻測量程序

• 打開所用主電路中有源晶振晶體單元的任一端,并將可變電阻器串聯插入晶體單元,如圖E所示.

• 更改電阻值以檢查當時觀察到的振蕩極限和電阻(歐姆).在這種情況下,必須打開和關閉電源電路.

• 電路中的負電阻(-R)是通過上述方法獲得的值與晶體的諧振電阻R1之和.

• 該測量應在工作頻率的上限和下限進行

下面介紹由晶體單元組成的典型振蕩電路.例如,使用的元素常數.

CL=(C1xC2)/C1+C2)+雜散電容

雜散電容可在2pF到6pF之間變化. 1. 當在C-MOS振蕩電路中使用時,電路圖中的Rd是必不可少的,以將驅動電平保持在規定值內并獲得穩定的振蕩頻率.

2. C1和C2應在10~31pF的范圍內使用.如果在低于或高于30pF的情況下使用C1和C2,則振蕩可能容易受到電路條件的影響,驅動電平可能增加或負電阻可能降低,從而導致不穩定的振蕩.

3. 晶體振蕩電路的布局應盡可能短

4. 應減少電路和接地圖案之間的雜散電容.

5. 應避免晶體振蕩電路圖案在其他電路圖案上的交叉.

6. 超聲波清潔可能導致有源晶振晶體單元的劣化.

.png)

圖A

除非在微處理器數據表中另有規定,否則本應用筆記可用作選擇晶振的一般指導,該晶體可與許多領先的微處理器制造商一起使用.

大多數微處理器都包括一個帶正反饋電阻(典型值為1MO)的逆變器設計,帶有一個可選的串聯電阻,其值在10歐姆到1K歐姆之間變化(見圖A)

它具有輸入端口(通常稱為XIN,XI,XTALI或類似性質)和輸出端口(XOUT,XO,XTALO或類似性質),用于這兩個端口之間的晶體單元連接.大多數芯片都設計有一個選項,可以通過外部時鐘振蕩器驅動,輸入到晶體輸入端口,也可以使用外部晶振.

根據共振頻率,可以選擇晶體作為基波或泛音模式.通常,28MHz以上的頻率需要第三個泛音模式以獲得價格優勢和交付.

在并聯模式中,石英晶振電抗是電感性的,需要兩個外部電容器(C1)和(C2)來實現必要的振蕩相移.無論晶體處于基模還是泛音模式,都需要C1和C2.C1和C2的值由芯片制造商規定,從6pF到47pF不等.

C1和C2可能不平衡,即值相等,但有時會以特定比率(C1/C2)偏移以獲得最佳性能,具體取決于晶體和放大器特性以及電路板布局.圖B示出了基模操作的典型配置.

在泛音模式中,需要附加電感器L1和電容Cc來選擇第三泛音模式,同時抑制或拒絕基模.選擇第三泛音晶體電路中的L1和Cc值以滿足以下條件.

來自串聯諧振電路的L1,Cc分量的頻率低于基頻,這使得電路看起來在基頻上是電感性的.這種情況不利于基模的振蕩.

來自并聯諧振電路的L1,Cc和C2分量的頻率大約在基波和第三泛音頻率之間的中間.這種情況使電路在第三泛音頻率處電容,這有利于在所需的泛音模式下的振蕩.(見圖C)

圖C

不同晶體頻率的L1典型值:

圖D

當晶體單元作為振蕩電路中的感應無功電抗被驅動時,晶體單元和振蕩電路之間的關系如圖E所示.為了改善振蕩電路的啟動條件,可以增加振蕩電路的值.負電阻-R-振蕩電路的哪個參數.如果沒有很多負電阻(較小的負電阻)的電路與具有較大諧振電阻的貼片晶振晶體單元組合,則起始條件將變得更糟.振蕩電路的設計目標應使負電阻值為諧振電阻的5至10倍. 還需要將負載電容的中心值(確定振蕩頻率的絕對值)和可變范圍(振蕩頻率的微調范圍)保持在振蕩電路中的最佳值.

負阻測量程序

• 打開所用主電路中有源晶振晶體單元的任一端,并將可變電阻器串聯插入晶體單元,如圖E所示.

• 更改電阻值以檢查當時觀察到的振蕩極限和電阻(歐姆).在這種情況下,必須打開和關閉電源電路.

• 電路中的負電阻(-R)是通過上述方法獲得的值與晶體的諧振電阻R1之和.

• 該測量應在工作頻率的上限和下限進行

正在載入評論數據...

相關資訊

- [2024-02-18]Greenray晶體振蕩器專為國防和航...

- [2024-01-20]HELE加高產品和技術及熱門應用

- [2024-01-20]HELE加高一個至關重要的組件晶體...

- [2023-12-28]Suntsu晶振最新的射頻濾波器突破...

- [2023-12-28]Qantek提供各種高可靠性微處理器...

- [2023-10-11]日本納卡石英晶體的低老化領先同...

- [2023-09-25]遙遙領先H.ELE開啟汽車創新

- [2023-09-23]瑞薩電子MCU和MPU產品領先同行

.png)